HI-3200, HI-3201

AVIONICS DATA MANAGEMENT ENGINE /

ARINC 429 - CAN BUS BRIDGE

September 2020

# **GENERAL DESCRIPTION**

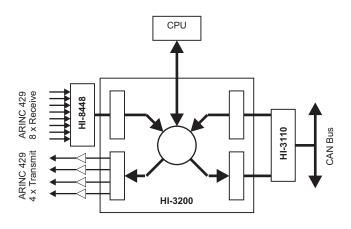

The HI-3200 from Holt Integrated Circuits is a single chip CMOS data management IC capable of managing, storing and forwarding avionics data messages between eight ARINC 429 receive channels, four ARINC 429 transmit channels and a single CAN / ARINC 825 data bus.

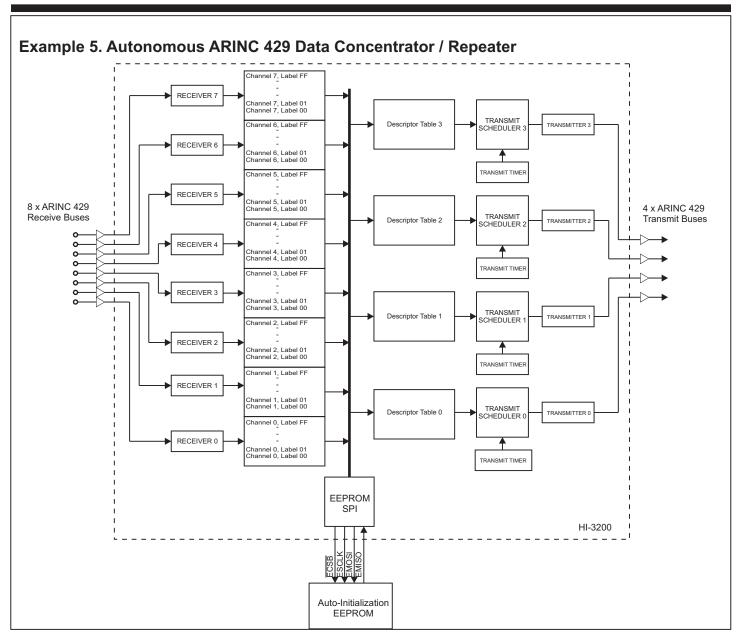

The ARINC 429 and CAN buses may be operated independently, allowing a host CPU to send and receive data on multiple buses, or the HI-3200 can be programmed to automatically re-format, re-label, re-packetize and retransmit data from ARINC 429 receive buses to ARINC 429 transmit buses, as well as from ARINC 429 to CAN or CAN to ARINC 429.

A 32K x 8 on-board memory allows received data to be logically organized and automatically updated as new ARINC 429 labels or CAN frames are received.

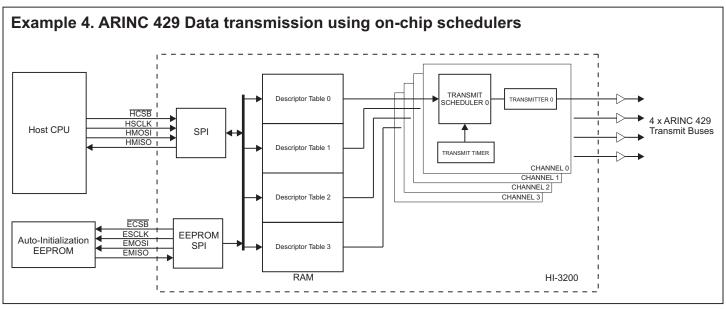

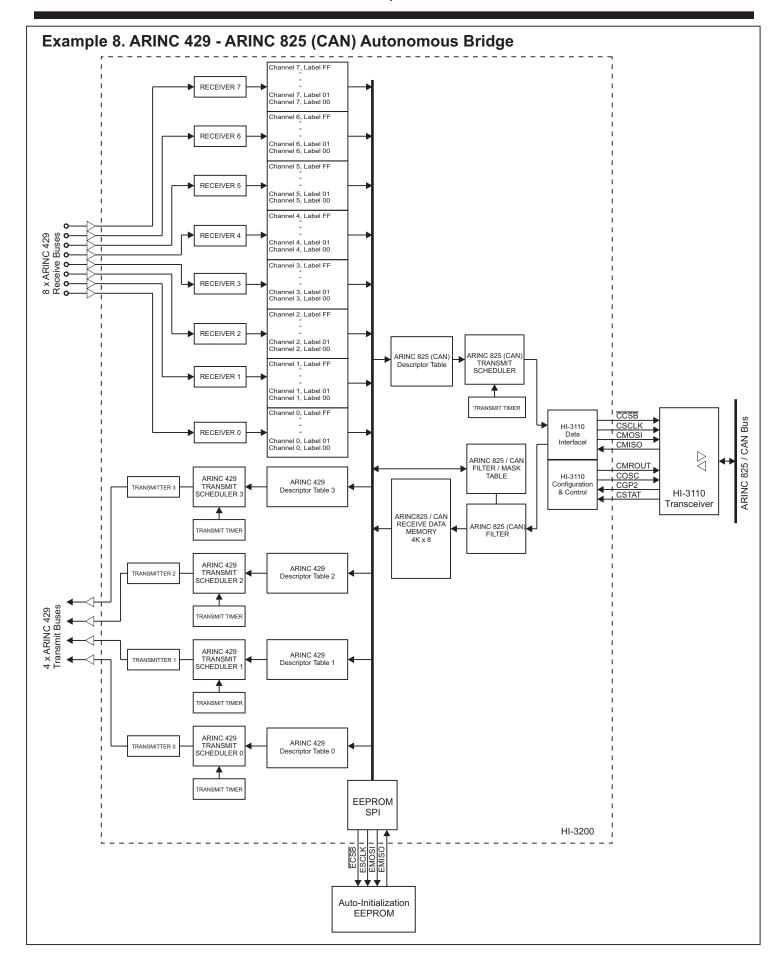

An auto-initialization feature allows configuration information to be up-loaded from an external EEPROM on reset to facilitate rapid start-up or operation without a host CPU.

The HI-3200 interfaces directly with Holt's HI-8448 octal ARINC 429 receiver IC, HI-8596 or HI-8592 ARINC 429 line drivers and HI-3110 integrated CAN controller / transceiver.

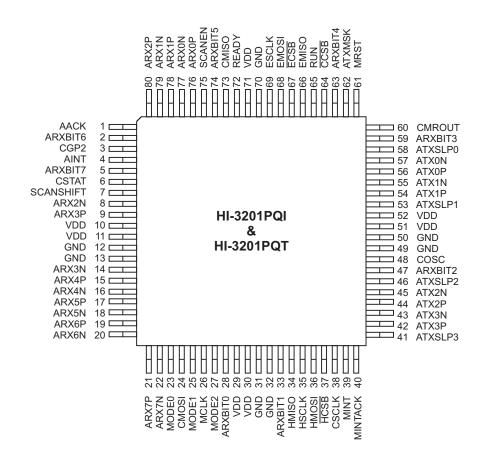

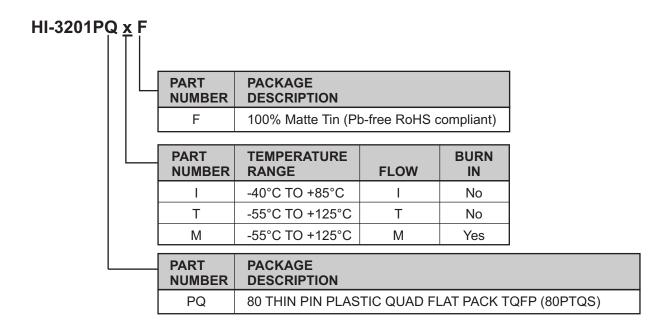

The HI-3201 is identical to the HI-3200 except it comes in an 80-pin PQFP package with eight instead of two ARINC 429 bit monitor pins.

# **APPLICATION**

### **FEATURES**

- Eight ARINC 429 Receive channels

- Four ARINC 429 Transmit channels

- CAN Bus / ARINC 825 Interface

- 32KB on chip user-configurable data storage memory

- Programmable received data filtering for ARINC 429 and CAN buses

- Programmable transmission schedulers for periodic ARINC 429 and CAN message broadcasting

- Flexible protocol bridge ARINC 429 to CAN and CAN to ARINC 429

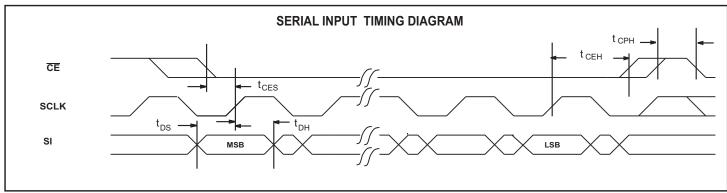

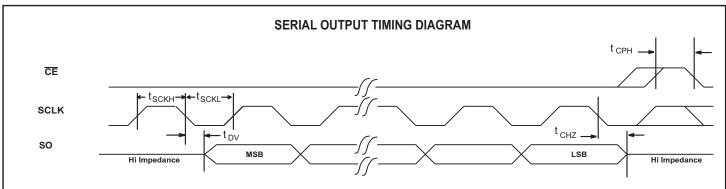

- SPI Host CPU interface

- Auto-initialization feature allows power-on configuration or independent operation without CPU

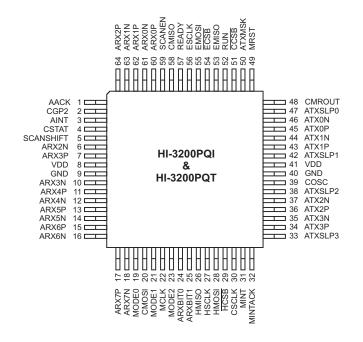

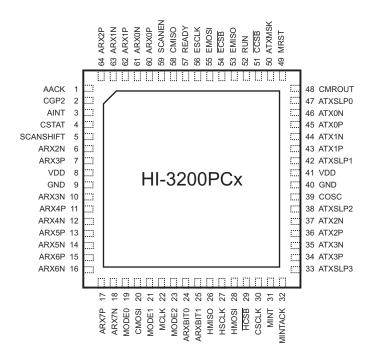

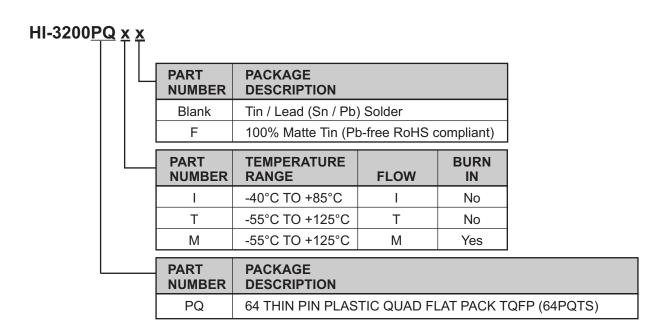

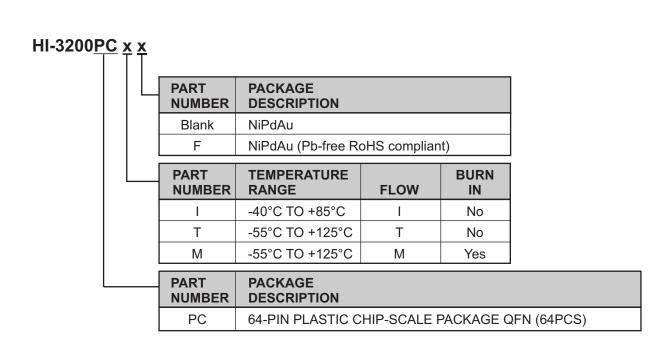

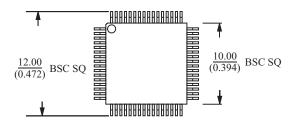

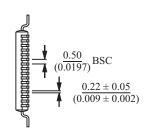

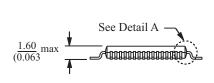

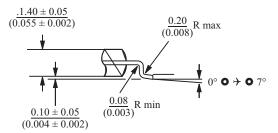

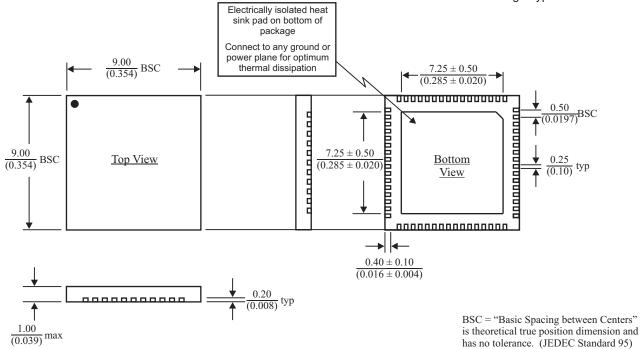

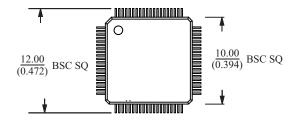

# PIN CONFIGURATION

64 - Pin Plastic Quad Flat Pack (PQFP)

(See ordering information for additional pin configurations)

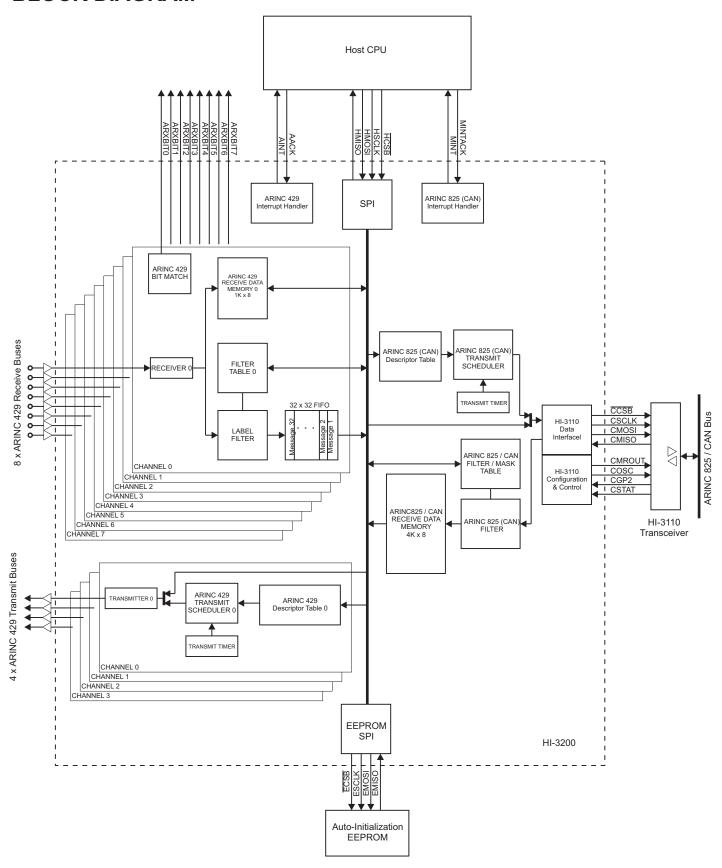

# **BLOCK DIAGRAM**

# **APPLICATION OVERVIEW**

The HI-3200 is a flexible device for managing ARINC 429 and ARINC 825 communications and data storage in many avionics applications. The device architecture centers around a 32K x 8 static RAM used for data storage, data filtering tables and table-driven transmission schedulers. Once configured, the device can operate autonomously without a host CPU, negating the need for software development or DO-178 certification. Configuration data may be uploaded into the device from an external EEPROM, following system reset.

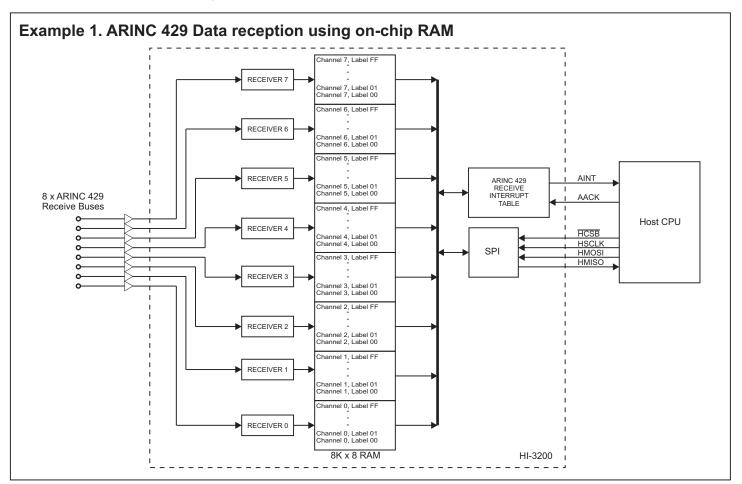

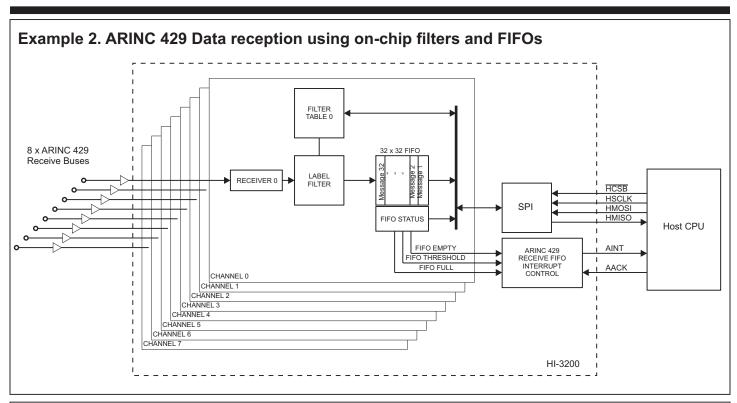

The device supports up to eight ARINC 429 receive channels. Received data is stored in on-chip RAM organized by channel number and label. The data table continually updates as new labels arrive. Programmable interrupts and filters alert the host subsystem to labels of interest.

Each ARINC 429 receive channel also includes a 32 message deep FIFO allowing selected label data to be queued for subsequent host access.

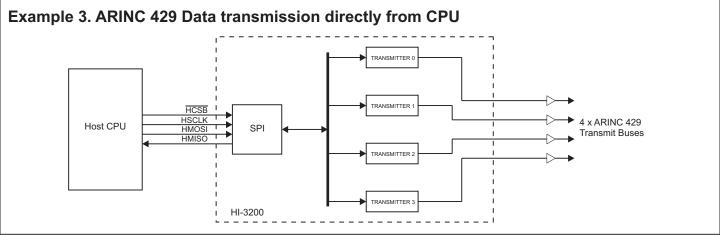

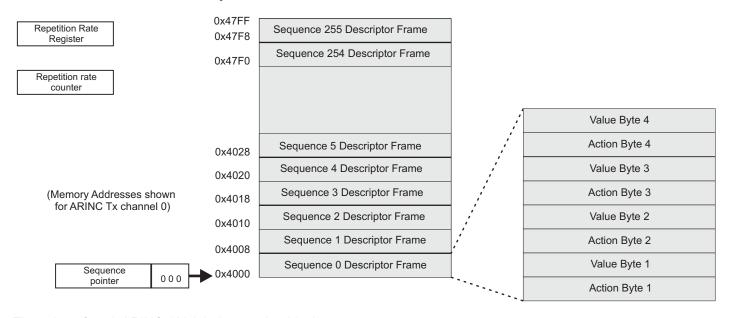

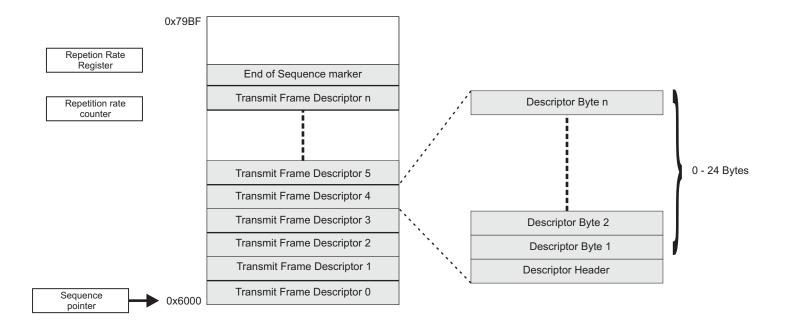

The HI-3200 includes four independent ARINC 429 transmit channels. Transmission may be controlled entirely by an external CPU, or autonomously by programming one or more of the four on-chip ARINC 429 transmit schedulers. These allow periodic transmission

to occur without CPU. Source data for transmission may be selected from RAM based tables of constants and / or from the received channel data. Powerful options exist for constructing ARINC 429 labels as well as controlling their timing and conditional transmission.

Even when running under the control of schedulers, the host CPU may insert new labels for transmission at will.

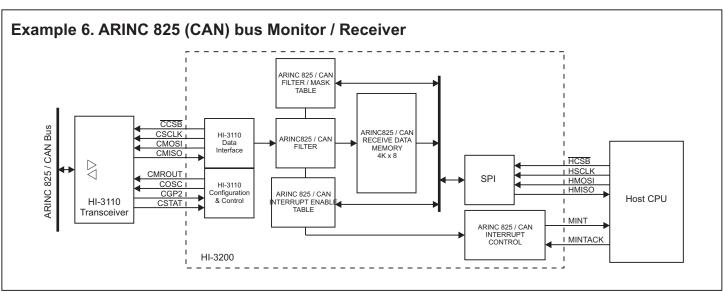

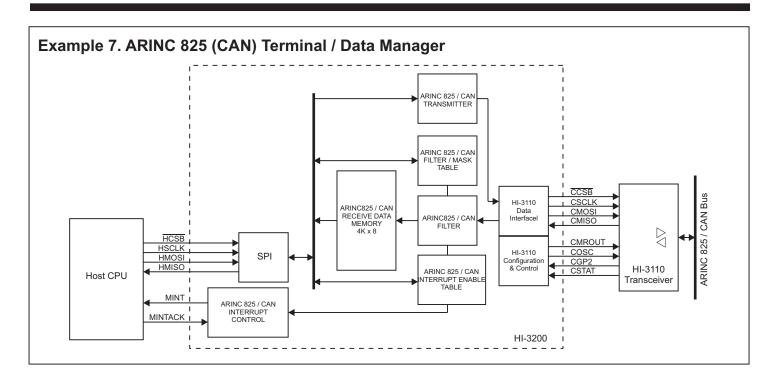

The HI-3200 also supports ARINC 825 (CAN) communication. An external HI-3110 CAN controller automatically handles the CAN bus protocol and physical interface. The HI-3200 configures the HI-3110 at system initialization and manages all traffic to and from the CAN bus.

As with ARINC 429, ARINC 825 received data may be filtered and stored in on-chip RAM, organized by ID field filters. ARINC 825 frame transmission may be directly controlled by a host CPU or by an on-chip transmission scheduler. CAN frames may be built and conditionally transmitted using the scheduler's flexible instruction set. Source data for CAN frames can be from CPU, stored constants or from received ARINC 429 data tables.

The following examples show eight possible configurations of how the HI-3200 may be used:

# PIN DESCRIPTIONS

| SIGNAL          | FUNCTION | DESCRIPTION                                                                                                                                                  | PULL UP/DOW |

|-----------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| AACK            | INPUT    | ARINC 429 Receiver Interrupt Acknowledge (Active High)                                                                                                       | Pull-Down   |

| AINT            | OUTPUT   | ARINC 429 Receiver Interrupt (Active High)                                                                                                                   |             |

| ARX0N           | INPUT    | ARINC 429 Rx negative data input for channel 0                                                                                                               |             |

| ARX0P           | INPUT    | ARINC 429 Rx positive data input for channel 0                                                                                                               |             |

| ARX1N           | INPUT    | ARINC 429 Rx negative data input for channel 1                                                                                                               |             |

| ARX1P           | INPUT    | ARINC 429 Rx positive data input for channel 1                                                                                                               |             |

| ARX2N           | INPUT    | ARINC 429 Rx negative data input for channel 2                                                                                                               |             |

| ARX2P           | INPUT    | ARINC 429 Rx positive data input for channel 2                                                                                                               |             |

| ARX3N           | INPUT    | ARINC 429 Rx negative data input for channel 3                                                                                                               |             |

| ARX3P           | INPUT    | ARINC 429 Rx positive data input for channel 3                                                                                                               |             |

| ARX4N           | INPUT    | ARINC 429 Rx negative data input for channel 4                                                                                                               |             |

| ARX4P           | INPUT    | ARINC 429 Rx positive data input for channel 4                                                                                                               |             |

| ARX5N           | INPUT    | ARINC 429 Rx negative data input for channel 5                                                                                                               |             |

| ARX5P           | INPUT    | · · · · · · · · · · · · · · · · · · ·                                                                                                                        |             |

|                 |          | ARINC 429 Rx positive data input for channel 5                                                                                                               |             |

| ARX6N           | INPUT    | ARINC 429 Rx negative data input for channel 6                                                                                                               |             |

| ARX6P           | INPUT    | ARINC 429 Rx positive data input for channel 6                                                                                                               |             |

| ARX7N           | INPUT    | ARINC 429 Rx negative data input for channel 7                                                                                                               |             |

| ARX7P           | INPUT    | ARINC 429 Rx positive data input for channel 7                                                                                                               |             |

| ARXBIT0-1       | OUTPUTS  | ARINC 429 received payload bit monitor pins 0 and 1                                                                                                          |             |

| ARXBIT2-7       | OUTPUTS  | ARINC 429 received payload bit monitor pins 2 through 7 (HI-3201 only)                                                                                       |             |

| ATX0N           | OUTPUT   | ARINC 429 Tx channel 0 negative data output to line driver                                                                                                   |             |

| ATX0P           | OUTPUT   | ARINC 429 Tx channel 0 positive data output to line driver                                                                                                   |             |

| ATX1N           | OUTPUT   | ARINC 429 Tx channel 1 negative data output to line driver                                                                                                   |             |

| ATX1P           | OUTPUT   | ARINC 429 Tx channel 1 positive data output to line driver                                                                                                   |             |

| ATX2N           | OUTPUT   | ARINC 429 Tx channel 2 negative data output to line driver                                                                                                   |             |

| ATX2P           | OUTPUT   | ARINC 429 Tx channel 2 positive data output to line driver                                                                                                   |             |

| ATX3N           | OUTPUT   | ARINC 429 Tx channel 3 negative data output to line driver                                                                                                   |             |

| ATX3P           | OUTPUT   | ARINC 429 Tx channel 3 positive data output to line driver                                                                                                   |             |

| ATXMSK          | INPUT    | Turn off ARINC 429 Transmit pins (Holds TXnA/B pins zero)                                                                                                    | Pull-Down   |

| ATXSLP0         | OUTPUT   | ARINC 429 Tx channel 0 data rate select output. 1 = high speed, 0 = low speed                                                                                | T dii Dowii |

| ATXSLP1         | OUTPUT   | ARINC 429 Tx channel 1 data rate select output. 1 = high speed, 0 = low speed                                                                                |             |

| ATXSLP2         | OUTPUT   | ARINC 429 Tx channel 2 data rate select output. 1 = high speed, 0 = low speed  ARINC 429 Tx channel 2 data rate select output. 1 = high speed, 0 = low speed |             |

|                 |          |                                                                                                                                                              |             |

| ATXSLP3<br>CCSB | OUTPUT   | ARINC 429 Tx channel 3 data rate select output. 1 = high speed, 0 = low speed                                                                                |             |

|                 | OUTPUT   | SPI chip select for HI-3110 CAN Controller / Transceiver                                                                                                     | D. II D     |

| CGP2            | INPUT    | Signal from HI-3110 CAN Controller / Transceiver indicating CAN Rx data is available                                                                         | Pull-Down   |

| CMISO           | INPUT    | SPI serial data input from HI-3110 CAN Controller / Transceiver                                                                                              | Pull-Down   |

| CMOSI           | OUTPUT   | SPI serial data output to HI-3110 CAN Controller / Transceiver                                                                                               |             |

| CMROUT          | OUTPUT   | Master Reset signal to HI-3110 CAN Controller / Transceiver                                                                                                  |             |

| COSC            | OUTPUT   | 24 MHz CAN reference clock output to HI-3110 CAN Controller / Transceiver                                                                                    |             |

| CSCLK           | OUTPUT   | SPI clock for HI-3110 CAN Controller / Transceiver                                                                                                           |             |

| CSTAT           | INPUT    | Signal from HI-3110 CAN Controller / Transceiver indicating CAN Tx FIFO is full                                                                              | Pull-Down   |

| ECSB            | OUTPUT   | SPI chip select for auto-initialization EEPROM                                                                                                               |             |

| EMISO           | INPUT    | SPI serial data input from auto-inialization EEPROM                                                                                                          | Pull-Down   |

| EMOSI           | OUTPUT   | SPI serial data output to auto-initialization EEPROM                                                                                                         |             |

| ESCLK           | OUTPUT   | SPI clock for auto-initialization EEPROM (8MHz max.)                                                                                                         |             |

| GND             | POWER    | Chip 0V supply                                                                                                                                               |             |

| HCSB            | INPUT    | Chip select. Data is shifted into HMOSI and out of HMISO when HCSB is low                                                                                    | Pull-Up     |

| HMISO           | OUTPUT   | Host CPU SPI interface serial data output                                                                                                                    |             |

| HMOSI           | INPUT    | Host CPU SPI interface serial data input                                                                                                                     | Pull-Down   |

| HSCLK           | INPUT    | SPI Clock. Data is shifted into or out of the SPI interface using HSCLK                                                                                      | Pull-Down   |

| MCLK            | INPUT    | Master 48 MHz (+/- 0.1%) reference clock for ARINC 429 and CAN bus bit timing                                                                                | Pull-Down   |

| MINT            | OUTPUT   | Programmable event interrupt output (Active High)                                                                                                            | . an bown   |

| MINTACK         | INPUT    | Programmable event interrupt acknowledge (Active High)                                                                                                       | Pull-Down   |

| MODE2:0         | INPUTS   | MODE2 through MODE0 define HI-3200 start-up and initialization mode                                                                                          | Pull-Downs  |

|                 |          |                                                                                                                                                              |             |

| MRST            | INPUT    | Master Reset to HI-3200 Active High. See RESET AND START-UP section                                                                                          | Pull-Down   |

| PROG (MODE0)    | INPUT    | Multiplexed with MODE0 pin, PROG initiates HI-3200 EEPROM Auto-Initialization                                                                                | Pull-Down   |

| READY           | OUTPUT   | READY goes high when post-RESET initialization is complete                                                                                                   | B " F       |

| RUN             | INPUT    | Master enable signal for ARINC 429 and CAN transmit schedulers                                                                                               | Pull-Down   |

| SCANEN          | RESERVED | Connect to GND                                                                                                                                               |             |

| SCANSHIFT       | RESERVED | Connect to GND                                                                                                                                               |             |

| VDD             | POWER    | 3.3V power supply                                                                                                                                            |             |

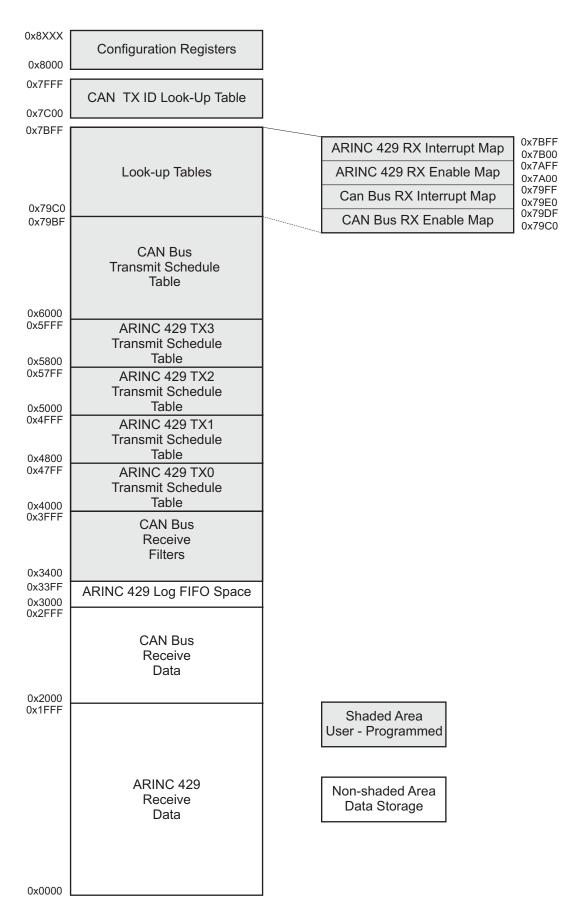

# HI-3200 MEMORY MAP

# HI-3200 REGISTER MAP

| ADDRESS | R/W  | REGISTER                          | MNEMONIC | DESCRIPTION                                      |

|---------|------|-----------------------------------|----------|--------------------------------------------------|

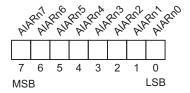

| 0x8000  | R*   | ARINC 429 Rx PENDING INTERRUPT    | APIR     | Defines channel(s) with pending Interrupt        |

| 0x8001  | R    | ARINC 429 Rx INTERRUPT ADDRESS 0  | AIAR0    | ARINC 429 Interrupt Vector channel 0             |

| 0x8002  | R    | ARINC 429 Rx INTERRUPT ADDRESS 1  | AIAR1    | ARINC 429 Interrupt Vector channel 1             |

| 0x8003  | R    | ARINC 429 Rx INTERRUPT ADDRESS 2  | AIAR2    | ARINC 429 Interrupt Vector channel 2             |

| 0x8004  | R    | ARINC 429 Rx INTERRUPT ADDRESS 3  | AIAR3    | ARINC 429 Interrupt Vector channel 3             |

| 0x8005  | R    | ARINC 429 Rx INTERRUPT ADDRESS 4  | AIAR4    | ARINC 429 Interrupt Vector channel 4             |

| 0x8006  | R    | ARINC 429 Rx INTERRUPT ADDRESS 5  | AIAR5    | ARINC 429 Interrupt Vector channel 5             |

| 0x8007  | R    | ARINC 429 Rx INTERRUPT ADDRESS 6  | AIAR6    | ARINC 429 Interrupt Vector channel 6             |

| 0x8008  | R    | ARINC 429 Rx INTERRUPT ADDRESS 7  | AIAR7    | ARINC 429 Interrupt Vector channel 7             |

| 0x8009  | _    | RESERVED                          |          | ·                                                |

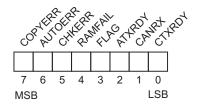

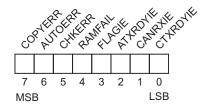

| 0x800A  | R*   | PENDING INTERRUPT REGISTER        | PIR      | Indicates Interrupt type                         |

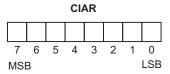

| 0x800B  | R    | INTERRUPT ADDRESS REGISTER        | CIAR     | CAN bus Interrupt vector                         |

| 0x800C  | R    | MUXED FIFO FLAGS                  | AMFF     | ARINC 429 Multiplexed FIFO flags                 |

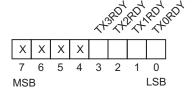

| 0x800D  | R    | ARINC 429 TX READY BITS           | ATRB     | ARINC 429 Transmitter Ready flags                |

| 0x800E  | R    | MASTER STATUS REGISTER            | MSR      | Indicates HI-3200 current status                 |

| 0x800F  | R/W  | MASTER CONTROL REGISTER           | MCR      | HI-3200 global configuration                     |

| 00040   | D/\/ | ADINO 400 DV CONTROL DECICEED O   | ADVO     | Occidental ADINO 400 consists also calculated to |

| 0x8010  | R/W  | ARING 429 RX CONTROL REGISTER 0   | ARXC0    | Configures ARINC 429 receive channel 0           |

| 0x8011  | R/W  | ARING 429 RX CONTROL REGISTER 1   | ARXC1    | Configures ARINC 429 receive channel 1           |

| 0x8012  | R/W  | ARING 429 RX CONTROL REGISTER 2   | ARXC2    | Configures ARINC 429 receive channel 2           |

| 0x8013  | R/W  | ARINC 429 RX CONTROL REGISTER 3   | ARXC3    | Configures ARINC 429 receive channel 3           |

| 0x8014  | R/W  | ARINC 429 RX CONTROL REGISTER 4   | ARXC4    | Configures ARINC 429 receive channel 4           |

| 0x8015  | R/W  | ARINC 429 RX CONTROL REGISTER 5   | ARXC5    | Configures ARINC 429 receive channel 5           |

| 0x8016  | R/W  | ARINC 429 RX CONTROL REGISTER 6   | ARXC6    | Configures ARINC 429 receive channel 6           |

| 0x8017  | R/W  | ARINC 429 RX CONTROL REGISTER 7   | ARXC7    | Configures ARINC 429 receive channel 7           |

| 0x8018  | R/W  | ARINC 429 TX CONTROL REGISTER 0   | ATXC0    | Configures ARINC 429 transmit channel 0          |

| 0x8019  | R/W  | ARINC 429 TX CONTROL REGISTER 1   | ATXC1    | Configures ARINC 429 transmit channel 1          |

| 0x801A  | R/W  | ARINC 429 TX CONTROL REGISTER 2   | ATXC2    | Configures ARINC 429 transmit channel 2          |

| 0x801B  | R/W  | ARINC 429 TX CONTROL REGISTER 3   | ATXC3    | Configures ARINC 429 transmit channel 3          |

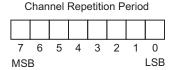

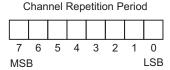

| 0x801C  | R/W  | ARINC 429 TX REPETITION RATE 0    | ATXRR0   | Sets sequence repeat time for ARINC TX0          |

| 0x801D  | R/W  | ARINC 429 TX REPETITION RATE 1    | ATXRR1   | Sets sequence repeat time for ARINC TX1          |

| 0x801E  | R/W  | ARINC 429 TX REPETITION RATE 2    | ATXRR2   | Sets sequence repeat time for ARINC TX2          |

| 0x801F  | R/W  | ARINC 429 TX REPETITION RATE 3    | ATXRR3   | Sets sequence repeat time for ARINC TX3          |

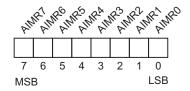

| 0x8020  | R/W  | ARINC 429 Rx INTERRUPT MASK       | AIMR     | Enables Interrupts on AINT pin                   |

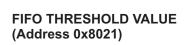

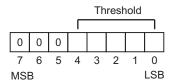

| 0x8021  | R/W  | ARINC 429 Rx FIFO THRESHOLD VALUE | AFTV     | Sets flag value for ARINC 429 Receive FIFO       |

| 0x8022  | R/W  | ARINC 429 LOOPBACK                | ALOOP    | Sets loop-back self-test mode                    |

| 0x8029  | R    | ARINC 429 Rx FIFO FULL FLAG       | AFFF     | Indicates which FIFOs are full                   |

| 0x802A  | R    | ARINC 429 Rx FIFO THRESHOLD FLAG  | AFTF     | Indicates which FIFOs hold > (thresh) messages   |

| 0x802B  | R    | ARINC 429 Rx FIFO NOT EMPTY FLAG  | FFNE     | Indicates which receive FIFOs hold data          |

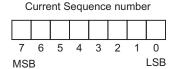

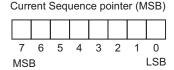

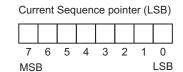

| 0x802C  | R    | ARINC 429 TX SEQUENCE POINTER 0   | ATXSP0   | Current address of ARINC transmit sequence 0     |

| 0x802D  | R    | ARINC 429 TX SEQUENCE POINTER 1   | ATXSP1   | Current address of ARINC transmit sequence 1     |

| 0x802E  | R    | ARINC 429 TX SEQUENCE POINTER 2   | ATXSP2   | Current address of ARINC transmit sequence 2     |

| 0x802F  | R    | ARINC 429 TX SEQUENCE POINTER 3   | ATXSP3   | Current address of ARINC transmit sequence 3     |

| 0x8030  | R/W  | CAN BUS BIT TIMING REGISTER 0     | CANBTR0  | Sets bit timing parameters for CAN bus           |

| 0x8031  | R/W  | CAN BUS BIT TIMING REGISTER 1     | CANBTR1  | Sets bit timing parameters for CAN bus           |

| 0x8032  | R/W  | CAN TRANSMIT CONTROL REGISTER     | CANTXC   | Controls CAN bus transmit scheduler              |

| 0x8033  | R/W  | CAN TX REPETITION RATE            | CANTXRR  | Sets sequence repeat time for CAN transmitter    |

| 0x8034  | R/W  | PENDING INTERRUPT ENABLE REGISTER | IMR      | Enables Interrupts on MINT pin                   |

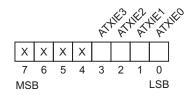

| 0x8035  | R/W  | ARINC 429 TX READY INT ENABLE     | ATRIE    | Enables ARINC 429 TX Ready Interrupts            |

| 0x803E  | R    | CAN TX SEQUENCE POINTER MSB       | CANTXSPH | High order CAN transmit sequence counter         |

| 0x803F  | R    | CAN TX SEQUENCE POINTER LSB       | CANTXSPL | Low order CAN transmit sequence counter          |

Fast Access Registers

Memory mapped register access only

<sup>\*</sup> Register is cleared when read (auto clear)

# HI-3200, HI-3201

| ADDRESS | R/W | REGISTER                         | MNEMONIC | DESCRIPTION                                  |

|---------|-----|----------------------------------|----------|----------------------------------------------|

| 0x805F  | R/W | PINS ARXBIT[7:0]                 | ARXBIT   | Values of pins ARXBIT[7:0]                   |

| 0x8060  | R/W | PIN ARXBITO CONFIG REG 1         | ARX0CR1  | ARINC 429 bit Monitor 0 channel & bit select |

| 0x8061  | R/W | PIN ARXBITO CONFIG REG 2         | ARX0CR2  | ARINC 429 bit Monitor 0 label select         |

| 0x8062  | R/W | PIN ARXBIT1 CONFIG REG 1         | ARX1CR1  | ARINC 429 bit Monitor 1 channel & bit select |

| 0x8063  | R/W | PIN ARXBIT1 CONFIG REG 2         | ARX1CR2  | ARINC 429 bit Monitor 1 label select         |

| 0x8064  | R/W | PIN ARXBIT2 CONFIG REG 1         | ARX2CR1  | ARINC 429 bit Monitor 2 channel & bit select |

| 0x8065  | R/W | PIN ARXBIT2 CONFIG REG 2         | ARX2CR2  | ARINC 429 bit Monitor 2 label select         |

| 0x8066  | R/W | PIN ARXBIT3 CONFIG REG 1         | ARX3CR1  | ARINC 429 bit Monitor 3 channel & bit select |

| 0x8067  | R/W | PIN ARXBIT3 CONFIG REG 2         | ARX3CR2  | ARINC 429 bit Monitor 3 label select         |

| 0x8068  | R/W | PIN ARXBIT4 CONFIG REG 1         | ARX4CR1  | ARINC 429 bit Monitor 4 channel & bit select |

| 0x8069  | R/W | PIN ARXBIT4 CONFIG REG 2         | ARX4CR2  | ARINC 429 bit Monitor 4 label select         |

| 0x806A  | R/W | PIN ARXBIT5 CONFIG REG 1         | ARX5CR1  | ARINC 429 bit Monitor 5 channel & bit select |

| 0x806B  | R/W | PIN ARXBIT5 CONFIG REG 2         | ARX5CR2  | ARINC 429 bit Monitor 5 label select         |

| 0x806C  | R/W | PIN ARXBIT6 CONFIG REG 1         | ARX6CR1  | ARINC 429 bit Monitor 6 channel & bit select |

| 0x806D  | R/W | PIN ARXBIT6 CONFIG REG 2         | ARX6CR2  | ARINC 429 bit Monitor 6 label select         |

| 0x806E  | R/W | PIN ARXBIT7 CONFIG REG 1         | ARX7CR1  | ARINC 429 bit Monitor 7 channel & bit select |

| 0x806F  | R/W | PIN ARXBIT7 CONFIG REG 2         | ARX7CR2  | ARINC 429 bit Monitor 7 label select         |

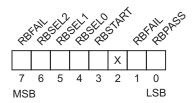

| 0x8070  | R/W | BIST CONTROL/STATUS              | BISTS    | Built-In Self-Test (bits 1,0 are read only)  |

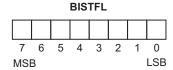

| 0x8071  | R   | BIST FAIL ADDRESS [7:0]          | BISTFL   | Low-order failing BIST memory address        |

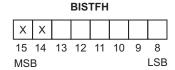

| 0x8072  | R   | BIST FAIL ADDRESS [12:8]         | BISTFH   | High-order failing BIST memory address       |

| 0x8073  | R   | AUTO-INIT FAIL LS ADDRESS [7:0]  | AIFL     | Auto-initialization fail address (low-byte)  |

| 0x8074  | R   | AUTO-INIT FAIL MS ADDRESS [15:8] | AIFH     | Auto-initialization fail address (high byte) |

### HI-3200 SYSTEM CONFIGURATION

Starting at memory address 0x8000, the HI-3200 contains a set of registers that are used to configure the HI-3200 device and, if used, its associated HI-3110 integrated CAN controller / transceiver.

The user needs only to program the HI-3200 configuration registers to completely define the full system operation.

Configuration information for the HI-3110 is automatically transferred from the HI-3200 to the HI-3110 immediately after the RUN input is asserted.

An SPI by-pass mode allows the user to directly access the HI-3110, but it is highly recommended that this is used solely for design debugging purposes and is locked out in the final design implementation. By-pass mode is enabled by setting the state of the MODE2:0 pins during reset. See the Reset and Start-Up Configuration section for more details.

The configuration registers are divided into four categories, as follows;

- 1. HI-3200 global configuration

- 2. ARINC 429 Receive channel configuration

- 3. ARINC 429 Transmit channel configuration

- 4. CAN Bus bit timing configuration

### **HI-3200 Global Configuration**

The following registers define the HI-3200 top-level configuration:

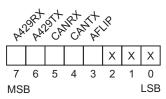

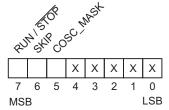

# MASTER CONTROL REGISTER (Address 0x800F)

| <u>Bit</u> | <u>Name</u> | R/W | <u>Default</u> | Description                                                                                                                                                                                                                                                         |

|------------|-------------|-----|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7          | A429RX      | R/W | 0              | This bit must be set to a "1" to allow the HI-3200 to receive ARINC 429 data on any of the eight channels. If set to a zero, the HI-3200 will not respond to any ARINC 429 receive bus, regardless of the state of the ARINC 429 Receive channel Control Registers. |

| 6          | A429TX      | R/W | 0              | This bit must be set to a "1" to allow the HI-3200 to transmit ARINC 429 data on any of the four channels. If set to a zero, the HI-3200 will not output ARINC 429 data and the ARINC 429 transmit sequencers will remain in their reset state.                     |

| 5          | CANRX       | R/W | 0              | This bit must be set to a "1" to allow the HI-3200 to receive CAN Frames from the HI-3110 controller. If set to a zero, the HI-3200 will not respond to any received CAN frames, regardless of the state of the CAN Bus Control Register.                           |

| 4          | CANTX       | R/W | 0              | This bit must be set to a "1" to allow the HI-3200 to transmit CAN frames. If set to a zero, the HI-3200 will not output CAN frames and the CAN transmit sequencer will remain in its reset state.                                                                  |

| 3          | AFLIP       | R/W | 0              | When set to a "1", this bit switches the bit order of the ARINC 429 label byte in both receive and transmit channels.                                                                                                                                               |

| 2          | -           | R/W | 0              | Not Used                                                                                                                                                                                                                                                            |

| 1          | -           | R/W | 0              | Not Used                                                                                                                                                                                                                                                            |

| 0          | -           | R/W | 0              | Not Used                                                                                                                                                                                                                                                            |

# **CAN Bus Timing Configuration**

Two registers must be programmed to define the CAN bus data rate and bit sampling segment times. This information is transferred directly to the HI-3110 CAN controller's BTR0 and BTR1 registers following the rising edge of the RUN input.

The HI-3110 OSCIN clock frequency must be set to achieve the desired bit rate. The HI-3200 COSC output signal provides a convenient 24MHz clock source for the HI-3110. For a full description of CAN Bus timing requirements, please refer to the Holt HI-3110 data sheet.

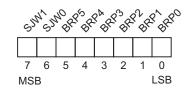

CANBTR0 (Address 0x8030)

CANBTR0 defines the value of the Re-synchronization Jump Width (SJW) and the Baud Rate Prescaler (BRP).

| <u>Bit</u> | <u>Name</u> | R/W | <u>Default</u> | <u>Description</u>                                                                                                                                                                                                                                                                                                                                        |  |

|------------|-------------|-----|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7:6        | SJW1:0      | R/W | 0              | These bits are used to compensate for phase shifts between different oscillators on the CAN bus. They define the maximum number of time quanta (Tq) a bit can be shortened or lengthened to allow the node to achieve re-synchronization to the edge of an incoming signal. Note that the time quantum (Tq) is the single unit of time within a bit time. |  |

| 5:0        | BRP5:0      | R/W | 0              | The baud rate prescaler relates the HI-3110 OSCIN clock frequency, fosc, to the CAN bit time as described in the HI-3110 data sheet.                                                                                                                                                                                                                      |  |

|            |             |     |                | BRP bits <5:0>                                                                                                                                                                                                                                                                                                                                            |  |

|            |             |     |                | 000000: BRP=1                                                                                                                                                                                                                                                                                                                                             |  |

|            |             |     |                | 000001: BRP=2                                                                                                                                                                                                                                                                                                                                             |  |

|            |             |     |                | 000010: BRP=3                                                                                                                                                                                                                                                                                                                                             |  |

|            |             |     |                | 000011: BRP=4                                                                                                                                                                                                                                                                                                                                             |  |

|            |             |     |                | etc.                                                                                                                                                                                                                                                                                                                                                      |  |

|            |             |     |                | 111111: BRP=64                                                                                                                                                                                                                                                                                                                                            |  |

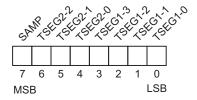

CANBTR1 (Address 0x8031)

CANBTR1 configures the CAN protocol bit timing segments in terms of time quanta (Tq) and sets the number of sampling points.

| <u>Bit</u> | <u>Name</u> | R/W | <u>Default</u> | Description                                                                                                                                                                   |  |  |

|------------|-------------|-----|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7          | SAMP        | R/W | 0              | This bit configures how many samples are taken per bit. $1 = \frac{1}{2}$ three samples/bit, $0 = \frac{1}{2}$ one sample/bit. Bit sampling occurs at the end of Phase Seg 1. |  |  |

|            |             |     |                | Note: ARINC825 states that there shall be only one sample per bit                                                                                                             |  |  |

| 5:0        | TSEG2-2:0   | R/W | 0              | Time segment 2 length. Tseg2 = Phase Seg2 of the CAN bit timing specification. Bits TSEG2-2:0 specify the number of time quanta in Phase Seg2.                                |  |  |

|            |             |     |                | Note: Not all combinations are valid, since Phase Seg2 must be greater than SJW.                                                                                              |  |  |

|            |             |     |                | TSEG2 bits <2:0>                                                                                                                                                              |  |  |

|            |             |     |                | 000: Not valid                                                                                                                                                                |  |  |

|            |             |     |                | 001: TSeg2 = 2 Tq clock cycles                                                                                                                                                |  |  |

|            |             |     |                | 010: TSeg2 = 3 Tq clock cycles                                                                                                                                                |  |  |

|            |             |     |                | etc.                                                                                                                                                                          |  |  |

111: TSeg2 = 8 Tq clock cycles

#### CANBTR1 cont.

| <u>Bit</u> | <u>Name</u> | R/W | <u>Default</u> | <u>Description</u>                                                                                                                                                                                                                                                                                                                        |  |

|------------|-------------|-----|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 5:0        | TSEG1-3:0   | R/W | 0              | Time segment 1 length. Tseg1 = Prop Seg + Phase Seg 1 of the CAN protocol bit time specification. Bits TSEG1-3:0 specify the number of time quanta in Prop Seg + Phase Seg Note: Not all combinations are valid since Prop Seg = Phase Seg1 >= Phase Seg2. The CA protocol states that the minimum number of Tq in a bit time shall be 8. |  |

|            |             |     |                | Note ARINC 825 states that the sample point shall not be less than 75% of the bit time. In this case, TSeg1 should be a minimum of $5Tq$ for Phase Seg2 (TSeg2) = $2Tq$ and SJW = $1Tq$ .                                                                                                                                                 |  |

|            |             |     |                | TSEG2 bits <2:0>                                                                                                                                                                                                                                                                                                                          |  |

|            |             |     |                | 0000: Not valid                                                                                                                                                                                                                                                                                                                           |  |

|            |             |     |                | 0001: TSeg1 = 2 Tq clock cycles                                                                                                                                                                                                                                                                                                           |  |

|            |             |     |                | 0010: TSeg1 = 3 Tq clock cycles                                                                                                                                                                                                                                                                                                           |  |

| etc.       |             |     |                | etc.                                                                                                                                                                                                                                                                                                                                      |  |

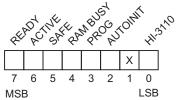

# **HI-3200 Operational Status Information**

The Master Status Register may be read at any time to determine the current operational state of the HI-3200:

1111: TSeg1 = 16 Tq clock cycles

# MASTER STATUS REGISTER (Address 0x800E)

| <u>Bit</u> | <u>Name</u> | R/W | <u>Default</u> | <u>Description</u>                                                                                                                                                                                                                      |

|------------|-------------|-----|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7          | READY       | R   | 0              | This bit is high, when the READY output pin is high, indicating that the part is able to accept and respond to host CPU SPI commands                                                                                                    |

| 6          | ACTIVE      | R   | 0              | This bit is high after RUN is asserted and the HI-3200 is in normal operating mode.                                                                                                                                                     |

| 5          | SAFE        | R   | 0              | This bit goes high when the part enters safe mode as a result of a Built-in Self-test fail or auto-initialization fail.                                                                                                                 |

| 4          | RAMBUSY     | R   | 0              | This is high during the time the RAM Integrity Check is running and RAM is clearing                                                                                                                                                     |

| 3          | PROG        | R   | 0              | Indicates that the HI-3200 is currently in the EEPROM programming cycle. Note that READY stays low until the cycle is complete.                                                                                                         |

| 2          | AUTOINIT    | R   | 0              | The HI-3200 is currently loading internal memory, registers and look-up tables from the Autoinitialization ${\sf EEPROM}$                                                                                                               |

| 1          | -           | R   | 0              | Notused                                                                                                                                                                                                                                 |

| 0          | HI-3110     | R   | 0              | The HI-3200 has detected the presence of an HI-3110 device connected to the CAN SPI port. <b>Note:</b> Only valid when RUN = 1 and CANTX and/or CANRX are enabled. After HI-3110 initialization this bit is not updated in Mode 6 or 7. |

# **ARINC 429 RECEIVE OPERATION**

The HI-3200 can receive ARINC 429 messages from up to eight ARINC 429 receive buses. External analog line receivers handle the physical layer connection

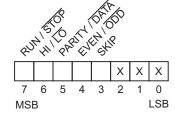

### **ARINC 429 Receive Channel Configuration**

Each of the eight possible ARINC 429 Receive channels is configured using its own Control Register. Register address 0x8010 controls ARINC 429 Receive channel #0, register address 0x8011 controls channel #1 and so on. ARINC 429 Receive Control Registers may be read at any time, but can only be written when the device is in the IDLE state (RUN input = "0", READY output = "1").

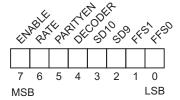

# ARINC 429 RX CONTROL REGISTER 0 - 7 (Address 0x8010 - 0x8017)

| <u>Bit</u> | <u>Name</u> | R/W | <u>Default</u> | <u>Description</u>                                                                                                                                                                                                                                                                |

|------------|-------------|-----|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7          | ENABLE      | R/W | 0              | This bit must be set to a "1" to enable ARINC 429 data reception on this channel.                                                                                                                                                                                                 |

| 6          | ਜਾਂ/LO      | R/W | 0              | Selects the ARINC 429 bit rate for the ARINC 429 receive channel. A "0" selects high-speed (100Kb/s) and a "1" selects low-speed (12.5Kb/s).                                                                                                                                      |

| 5          | PARITYEN    | R/W | 0              | When this bit is a one, the 32nd received ARINC bit is overwritten with a parity flag. The flag bit is set to a zero when the received ARINC word, including its parity bit has an odd number of ones. When PARITYEN is a zero, all 32-bits are received without parity checking. |

| 4          | DECODER     | R/W | 0              | When DECODER is a "1", bits 9 and 10 of ARINC 429 words received on this channel must match the SD9 and SD10 bits in the register. ARINC words received that do not match the SD conditions are ignored.                                                                          |

| 3          | SD10        | R/W | 0              | If DECODER is set to a "1", then this bit must match the received ARINC word bit 10 for the word to be accepted.                                                                                                                                                                  |

| 2          | SD9         | R/W | 0              | If DECODER is set to a "1", then this bit must match the received ARINC word bit 9 for the word to be accepted.                                                                                                                                                                   |

| 1-0        | FFS1:0      | R/W | 0              | FFS1 and FFS0 define when this channel's FIFO Flag is set, as shown below. The FIFO Flag will be set in the ARINC 429 Muxed FIFO Flags Register (0x800C). Bit 0 is receive channel 0 FIFO Flag, bit 1 is receive channel 1 FIFO Flag, bit 2 is receive channel 2 FIFO Flag, etc.  |

| FFS1 | FFS0 | FLAG set condition                   |

|------|------|--------------------------------------|

| 0    | 0    | FLAG never set                       |

| 0    | 1    | Set FLAG if FIFO NOT EMPTY bit = "1" |

| 1    | 0    | Set FLAG if FIFO > Threshold value   |

| 1    | 1    | Set FLAG is FIFO FULL bit "1"        |

|      |      |                                      |

#### **ARINC 429 Received Data Management**

The HI-3200 supports eight ARINC 429 receive buses using on-chip receivers to handle the protocol validation. The eight ARINC 429 RX Control Registers, ARXC0 - 7, define the characteristics of each receive channel.

The ARINC 429 receive function of the HI-3200 is activated by setting the A429RX bit in the Master Control Register.

When an ARINC 429 message is received by the HI-3200 on any bus, it is checked for protocol compliance. Messages with incorrect encoding are rejected.

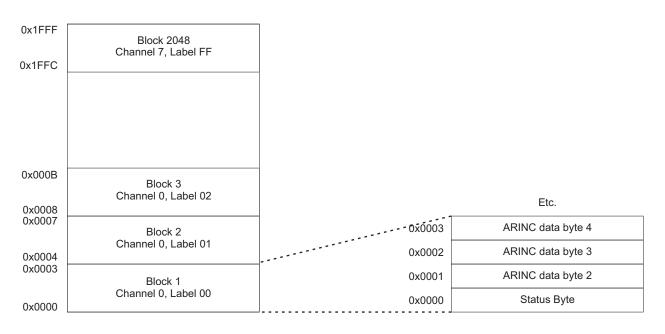

The HI-3200 contains an 8K byte memory for storing ARINC 429 received data. The memory is organized by channel number and ARINC 429 label value. Four bytes of memory are dedicated to each channel / label to store the 32-word ARINC 429 message.

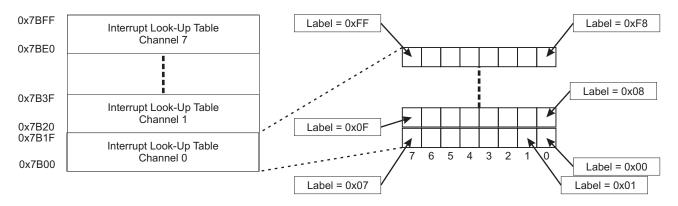

A look-up table is used to enable an interrupt on receipt of a new ARINC 429 message. Look-up table bit positions preloaded with a "1" will cause an Interrupt to be generated.

When a message is received that triggers an Interrupt, that channel's Interrupt bit is set in the ARINC 429 Receive Pending Interrupt Register. If this bit is unmasked in the ARINC 429 Receive Interrupt Mask Register, the AINT output pin is asserted. The label number of the ARINC 429 message causing the interrupt is loaded into that channel's ARINC 429 Receive Interrupt Address Register (AIARO - AIAR7).

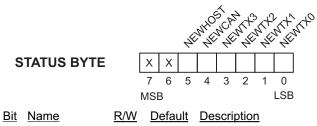

Because the ARINC Receive Memory is organized by label value, it is not necessary to store the received label value (first eight bits of the ARINC message) in the memory. Instead, the first byte is used to store a status byte.

The six active bits of the status byte are set to "1" when a new ARINC word is stored in the memory. These bits flag the ARINC word as new when the location is interrogated by the host CPU, any of the four ARINC 429 transmit schedulers or the CAN Bus transmit scheduler.

#### **ARINC 429 Received Data Memory Organization**

# **ARINC 429 Received Data Interrupt Look-Up Table**

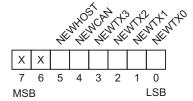

# **ARINC 429 Received Data Status Byte Definition**

| BIL | <u>iname</u> | K/VV | Default | Description                                                                                                                                                           |

|-----|--------------|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | -            | R/W  | 0       | Notused                                                                                                                                                               |

| 6   | -            | R/W  | 0       | Notused                                                                                                                                                               |

| 5   | NEWHOST      | R/W  | 0       | This bit is set when a new ARINC 429 word is received and stored in this block. It is reset when the host CPU executes SPI instruction $0xC0-0xFF$ to read the block. |

| 4   | NEWCAN       | R/W  | 0       | This bit is set when a new ARINC 429 word is received and stored in this block. It is reset when the CAN Transmit scheduler reads any bytes from the block.           |

| 3   | NEWTX3       | R/W  | 0       | This bit is set when a new ARINC 429 word is received and stored in this block. It is reset when the ARINC 429 Transmit scheduler #3 reads any bytes from the block.  |

| 2   | NEWTX2       | R/W  | 0       | This bit is set when a new ARINC 429 word is received and stored in this block. It is reset when the ARINC 429 Transmit scheduler #2 reads any bytes from the block.  |

| 1   | NEWTX1       | R/W  | 0       | This bit is set when a new ARINC 429 word is received and stored in this block. It is reset when the ARINC 429 Transmit scheduler #1 reads any bytes from the block.  |

| 0   | NEWTX0       | R/W  | 0       | This bit is set when a new ARINC 429 word is received and stored in this block. It is reset when the ARINC 429 Transmit scheduler #0 reads any bytes from the block.  |

### ARINC 429 Received Data Log FIFO

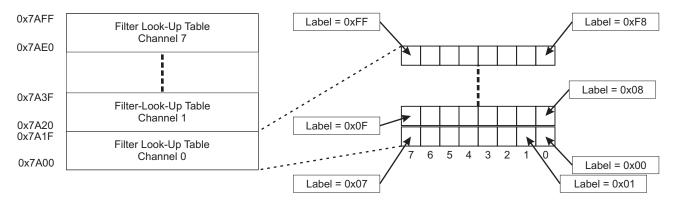

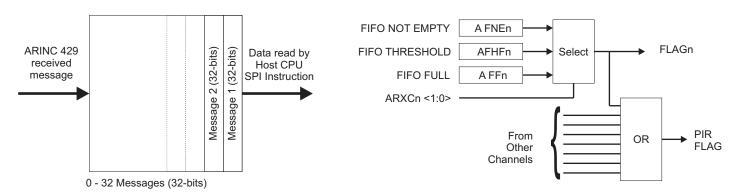

A 1K x 8 block of memory located between 0x3000 and 0x33FF is reserved for a set of eight ARINC 429 received data FIFOs. There is one FIFO for each ARINC 429 received data channel. Each FIFO can hold up to 32 ARINC 429 32-bit messages.

A look-up table driven filter defines which ARINC 429 messages are stored in each FIFO. The look-up table is initialized by the user with a "1" for each bit position corresponding to a selected channel / label combination. The look-up table is located at memory address 0x7A00.

When a new ARINC 429 message is received that meets the programmed conditions for acceptance (Enable look-up table bit = "1"), it is written into the channel's Receive Data FIFO. The contents of the FIFO may be read by the host CPU using dedicated FIFO read SPI Instructions.

The status of each channel's FIFOs is monitored by three FIFO status registers: FIFO NOT EMPTY, FIFO THRESHOLD, and FIFO FULL. One bit of each register reflects the current status of each FIFO.

The FIFOs are empty following reset. All three status registers are cleared. When an ARINC 429 message is written to a FIFO, its FIFO NOT EMPTY bit is set to a "1". When the FIFO contains more than the user-defined

number of messages as programmed in the ARINC FIFO THRESHOLD VALUE register, its FIFO THRESHOLD bit is set. If the FIFO is allowed to accumulate 32 messages, its FIFO FULL bit is set. Once a FIFO is full, subsequent messages continue to be written to the FIFO, and the oldest message is lost.

The user may generate an Interrupt by enabling one of the three FIFO status register bits to assert the FLAG bit in the Pending Interrupt Register. ARINC 429 Control Register bits 1:0 select the condition to trigger the FLAG interrupt.

The FIFO feature is particularly useful if the application wishes to accumulate sequential ARINC 429 messages of the same label value before reading them. The regular ARINC 429 receive data memory will, of course, overwrite messages of the same label value if a new message is received before the host CPU extracts the data.

**NOTE:** If the host reads a FIFO message at the same instant a new message is loaded into the FIFO from the protocol logic of the same receiver channel, the host may read a duplicate message. No messages are lost. The host may ignore the duplicate message or avoid this situation entirely by using RAM for received data storage or using interrupts to ensure host reads do not coincide with received messages.

### ARINC 429 Received Data Enable Look-Up Table

#### ARINC 429 Received Data FIFO (x8)

# **ARINC 429 Received Data FIFO Status Registers**

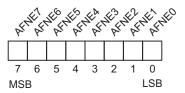

# FIFO NOT EMPTY REGISTER (Address 0x802B)

| <u>Bit</u> | <u>Name</u> | R/W | <u>Default</u> | <u>Description</u>                                                        |

|------------|-------------|-----|----------------|---------------------------------------------------------------------------|

| 7          | AFNE7       | R   | 0              | This bit is set to "1" if FIFO #7 contains at least one ARINC 429 message |

| 6          | AFNE6       | R   | 0              | This bit is set to "1" if FIFO #6 contains at least one ARINC 429 message |

| 5          | AFNE5       | R   | 0              | This bit is set to "1" if FIFO #5 contains at least one ARINC 429 message |

| 4          | AFNE4       | R   | 0              | This bit is set to "1" if FIFO #4 contains at least one ARINC 429 message |

| 3          | AFNE3       | R   | 0              | This bit is set to "1" if FIFO #3 contains at least one ARINC 429 message |

| 2          | AFNE2       | R   | 0              | This bit is set to "1" if FIFO #2 contains at least one ARINC 429 message |

| 1          | AFNE1       | R   | 0              | This bit is set to "1" if FIFO #1 contains at least one ARINC 429 message |

| 0          | AFNE0       | R   | 0              | This bit is set to "1" if FIFO #0 contains at least one ARINC 429 message |

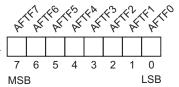

# FIFO THRESHOLD REGISTER (Address 0x802A)

| <u>Bit</u> | <u>Name</u> | <u>R/W</u> | <u>Default</u> | <u>Description</u>                                                                  |

|------------|-------------|------------|----------------|-------------------------------------------------------------------------------------|

| 7          | AFTF7       | R          | 0              | This bit is set to "1" if FIFO #7 contains > threshold number of ARINC 429 messages |

| 6          | AFTF6       | R          | 0              | This bit is set to "1" if FIFO #6 contains > threshold number of ARINC 429 messages |

| 5          | AFTF5       | R          | 0              | This bit is set to "1" if FIFO #5 contains > threshold number of ARINC 429 messages |

| 4          | AFTF4       | R          | 0              | This bit is set to "1" if FIFO #4 contains > threshold number of ARINC 429 messages |

| 3          | AFTF3       | R          | 0              | This bit is set to "1" if FIFO #3 contains > threshold number of ARINC 429 messages |

| 2          | AFTF2       | R          | 0              | This bit is set to "1" if FIFO #2 contains > threshold number of ARINC 429 messages |

| 1          | AFTF1       | R          | 0              | This bit is set to "1" if FIFO #1 contains > threshold number of ARINC 429 messages |

| 0          | AFTF0       | R          | 0              | This bit is set to "1" if FIFO #0 contains > threshold number of ARINC 429 messages |

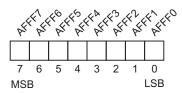

# FIFO FULL REGISTER (Address 0x8029)

| <u>Bit</u> | <u>Name</u> | <u>R/W</u> | <u>Default</u> | <u>Description</u>                                               |

|------------|-------------|------------|----------------|------------------------------------------------------------------|

| 7          | AFFF7       | R/W        | 0              | This bit is set to "1" if FIFO #7 contains 32 ARINC 429 messages |

| 6          | AFFF6       | R/W        | 0              | This bit is set to "1" if FIFO #6 contains 32 ARINC 429 messages |

| 5          | AFFF5       | R/W        | 0              | This bit is set to "1" if FIFO #5 contains 32 ARINC 429 messages |

| 4          | AFFF4       | R/W        | 0              | This bit is set to "1" if FIFO #4 contains 32 ARINC 429 messages |

| 3          | AFFF3       | R/W        | 0              | This bit is set to "1" if FIFO #3 contains 32 ARINC 429 messages |

| 2          | AFFF2       | R/W        | 0              | This bit is set to "1" if FIFO #2 contains 32 ARINC 429 messages |

| 1          | AFFF1       | R/W        | 0              | This bit is set to "1" if FIFO #1 contains 32 ARINC 429 messages |

| 0          | AFFF0       | R/W        | 0              | This bit is set to "1" if FIFO #0 contains 32 ARINC 429 messages |

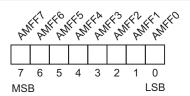

# ARINC 429 Muxed FIFO Flags Register (Address 0x800C)

| Bit | <u>Name</u> | R/W | <u>Default</u> | <u>Description</u>                                                                                                                                                                  |

|-----|-------------|-----|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | AMFF7       | R   | 0              | This bit gives the FIFO Flag Status for ARINC 429 Receive Channel 7. The FIFO Flag Status is set according to the value of the FFS[1:0] bits in the ARINC 429 Rx Control Register 7 |

| 6   | AMFF6       | R   | 0              | This bit gives the FIFO Flag Status for ARINC 429 Receive Channel 6. The FIFO Flag Status is set according to the value of the FFS[1:0] bits in the ARINC 429 Rx Control Register 6 |

| 5   | AMFF5       | R   | 0              | This bit gives the FIFO Flag Status for ARINC 429 Receive Channel 5. The FIFO Flag Status is set according to the value of the FFS[1:0] bits in the ARINC 429 Rx Control Register 5 |

| 4   | AMFF4       | R   | 0              | This bit gives the FIFO Flag Status for ARINC 429 Receive Channel 4. The FIFO Flag Status is set according to the value of the FFS[1:0] bits in the ARINC 429 Rx Control Register 4 |

| 3   | AMFF3       | R   | 0              | This bit gives the FIFO Flag Status for ARINC 429 Receive Channel 3. The FIFO Flag Status is set according to the value of the FFS[1:0] bits in the ARINC 429 Rx Control Register 3 |

| 2   | AMFF2       | R   | 0              | This bit gives the FIFO Flag Status for ARINC 429 Receive Channel 2. The FIFO Flag Status is set according to the value of the FFS[1:0] bits in the ARINC 429 Rx Control Register 2 |

| 1   | AMFF1       | R   | 0              | This bit gives the FIFO Flag Status for ARINC 429 Receive Channel 1. The FIFO Flag Status is set according to the value of the FFS[1:0] bits in the ARINC 429 Rx Control Register 1 |

| 0   | AMFF0       | R   | 0              | This bit gives the FIFO Flag Status for ARINC 429 Receive Channel 0. The FIFO Flag Status is set according to the value of the FFS[1:0] bits in the ARINC 429 Rx Control Register 0 |

## **ARINC 429 FIFO Threshold Value Register**

Default = 0x10

| Threshold Value | <u>Description</u>                                                                   |

|-----------------|--------------------------------------------------------------------------------------|

| 00000           | Threshold flag is set if at least 1 message is in FIFO (Same as FIFO NOT EMPTY FLAG) |

| 00001           | Threshold flag is set if more than one message are in the FIFO                       |

| 00010           | Threshold flag is set if more than two messages are in the FIFO                      |

| 00011           | Threshold flag is set if more than three messages are in the FIFO                    |

| 10000           | Threshold flag is set if more than sixteen messages are in the FIFO (default)        |

| 11111           | Threshold flag is set if 32 messages are in the FIFO (Same as FIFO FULL FLAG)        |

### **ARINC 429 Loop-back Self-Test**

The HI-3200 includes an ARINC 429 loop-back feature, which allows users to exercise the ARINC 429 transmit and receive channels for self-test purposes. The ARINC 429 Loop-Back register, ALOOP defines which receiver channels are in loop-back mode. When a "1" is programmed in the ALOOP bit position for a receiver, then its ARINC 429 bus connection to the external pins is broken and instead the input is connected to one of the four ARINC 429 transmit channels. Transmit channel 0 is connected to receive channel 0 and 1, transmit channel 1 is connected to receive channels 2 and 3, and so on.

When in loop-back mode, incoming ARINC 429 messages are ignored by the HI-3200. When running in loop-back mode the ARINC 429 transmit pins may be disabled by pulling the TXMSK input high. This prevents test messages from being output to the external ARINC 429 transmit buses.

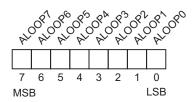

### **ARINC 429 LOOPBACK** (Address 0x8022)

| <u>Bit</u> | <u>Name</u> | R/W | <u>Default</u> | <u>Description</u>                                                      |

|------------|-------------|-----|----------------|-------------------------------------------------------------------------|

| 7          | ALOOP7      | R/W | 0              | This bit is set to "1" to loop-back transmit channel 3 to receiver 7 $$ |

| 6          | ALOOP6      | R/W | 0              | This bit is set to "1" to loop-back transmit channel 3 to receiver 6 $$ |

| 5          | ALOOP5      | R/W | 0              | This bit is set to "1" to loop-back transmit channel 2 to receiver $5$  |

| 4          | ALOOP4      | R/W | 0              | This bit is set to "1" to loop-back transmit channel 2 to receiver 4 $$ |

| 3          | ALOOP3      | R/W | 0              | This bit is set to "1" to loop-back transmit channel 1 to receiver 3 $$ |

| 2          | ALOOP2      | R/W | 0              | This bit is set to "1" to loop-back transmit channel 1 to receiver 2 $$ |

| 1          | ALOOP1      | R/W | 0              | This bit is set to "1" to loop-back transmit channel 0 to receiver 1 $$ |

| 0          | ALOOP0      | R/W | 0              | This bit is set to "1" to loop-back transmit channel 0 to receiver 0 $$ |

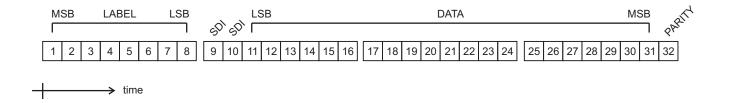

### ARINC 429 Bit ordering

ARINC 429 messages consist of a 32-bit sequence as shown below. The first eight bits that appear on the ARINC 429 bus are the label byte. The next twenty three bits comprise a data field which presents data in a variety of formats defined in the ARINC 429 specification. The last bit transmitted is an odd parity bit.

The HI-3200 stores the received message as four bytes. The bytes are stored in memory in little-endian order. That is to say, the label byte (or status byte) is stored at the lowest memory address, the byte representing received bits 9 through 16 is stored at the next address, the byte representing bits 17 through 24 at the next address and the byte representing bits 25 though 32 at the highest address.

The ARINC 429 specifies the MSB of the label as ARINC bit 1. Conversely, the data field MSB is bit 31. So the bit significance of the label byte and data fields are opposite.

The HI-3200 may be programmed to "flip" the bit ordering of the label byte as soon as it is received and immediately prior to transmission. This is accomplished by setting the AFLIP bit to a "1" in the Master Control Register. Note that once the label byte has been flipped, the HI-3200 handles the flipped data byte "post-flip" for the purpose of label interrupt matching, filtering and storage.

> 26 27 19

> > 10

#### ARINC 429 Message as received / transmitted on the ARINC 429 serial bus

#### ARINC 429 Message as stored in HI-3200 memory

| Byte 3 | 32 | 31 | 30 | 29 | 28   | 27    | 26 | 25 |   | 32 | 31 | 30 | 29 | 28 | 2  |

|--------|----|----|----|----|------|-------|----|----|---|----|----|----|----|----|----|

| Byte 2 | 24 | 23 | 22 | 21 | 20   | 19    | 18 | 17 | ĺ | 24 | 23 | 22 | 21 | 20 | 19 |

| Byte 1 | 16 | 15 | 14 | 13 | 12   | 11    | 10 | 9  | [ | 16 | 15 | 14 | 13 | 12 | 1  |

| Byte 0 | 1  | 2  | 3  | 4  | 5    | 6     | 7  | 8  |   | 8  | 7  | 6  | 5  | 4  | 3  |

|        |    |    |    | Α  | FLIF | P = " | 1" |    |   |    |    |    |    |    |    |

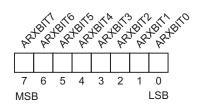

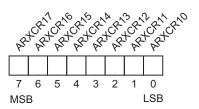

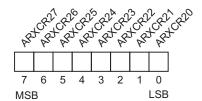

#### **ARINC 429 Bit Monitor Pins**

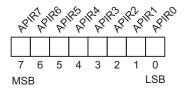

The HI-3200 has the capability of externally monitoring any ARINC 429 received payload bit through the pins ARXBIT[7:0] (**Note:** The HI-3200 provides external monitoring of two bits through pins ARXBIT1 and ARXBIT0, whereas the HI-3201 provides external monitoring of eight bits through pins ARXBIT7 to ARXBIT0). When the appropriate ARINC 429 receiver is enabled and the target label is received, the monitored bit value will be reflected on the pin. This allows the user to monitor any ARINC 429

received payload bit without performing any host SPI reads. The following registers configure the functionality of these monitor pins. Note that all these control register bits are reset to zero.

# PINS ARXBIT[7:0] REGISTER (Address 0x805F)

| <u>Bit</u> | <u>Name</u> | <u>R/W</u> | <u>Default</u> | <u>Description</u>                                                                                                                                                                                                                                                                              |

|------------|-------------|------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0        | ARXBIT[7:0] | R/W        | 0              | These bits reflect the value of the corresponding pins ARXBIT[7:0]. After reset, all values are zero. When a monitored ARINC 429 bit changes, this register is updated with the value, which is reflected on the corresponding pin. The purpose of this register is to allow the user to preset |

| the        |             |            |                | ARXBIT values after chip reset.                                                                                                                                                                                                                                                                 |

# PIN ARXBITO CONFIGURATION REGISTER 1 (Address 0x8060)

| <u>Bit</u> | <u>Name</u> | R/W | <u>Default</u> | <u>Description</u>                                                                                                                                                                                                                                                                                                                                               |

|------------|-------------|-----|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5        | ARXCR1[7:5] | R/W | 0              | These bits select which receive channel (0 through 7) will have bits monitored and reflected on the pin ARXBIT0.                                                                                                                                                                                                                                                 |

| 4:0        | ARXCR1[4:0] | R/W | 0              | These bits select which bit (8 through 31) of the ARINC payload will be reflected on the pin ARXBIT0. The receiver is specified by bits ARX0CR1[7:5] and the target label is specified by pin ARXBIT0 Configuration Register 2 described below. Note that bits 0 through 7 of the ARINC payload are not monitored and selecting these bits results in no effect. |

# PIN ARXBITO CONFIGURATION REGISTER 2 (Address 0x8061)

| <u>Bit</u> | <u>Name</u> | <u>R/W</u> | <u>Default</u> | <u>Description</u>                                                                                                                                                                                                          |

|------------|-------------|------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0        | ARXCR2[7:0] | R/W        | 0              | These bits select which label (0 through 255) will have bits monitored and reflected on the pin ARXBIT0. The receive channel and specific bits monitored are specified in ARXBIT0 Configuration Register 1 described above. |

# PINS ARXBIT1 Through ARXBIT7 CONFIGURATION REGISTERS (Addresses 0x8062 to 0x806F)

Each pin ARXBIT1 through ARXBIT7 are also specified by a pair of configuration registers similar to ARXBIT0 described above. Functionality is exactly the same. The register addresses for each pin specification are listed in the Register Map section (see page 11). Note that HI-3200 provides external monitoring of two bits through pins ARXBIT1 and ARXBIT0, whereas the HI-3201 provides external monitoring of eight bits through pins ARXBIT7 to ARXBIT0.

### CAN BUS RECEIVE OPERATION

The HI-3200 can receive CAN frames from a single CAN bus using an external HI-3110 IC to handle the CAN bus protocol and physical layer connection

### **CAN Received Data Management**

The HI-3200 interfaces to a CAN bus using an external HI-3110 CAN Controller / Transceiver IC. Communication between the HI-3200 and HI-3110 is handled by a dedicated high speed serial SPI link. Configuration parameters are automatically downloaded to the HI-3110 following a positive edge of the RUN input signal.

The HI-3110 handles all aspects of the CAN protocol as well as the physical layer interface to the CAN bus.

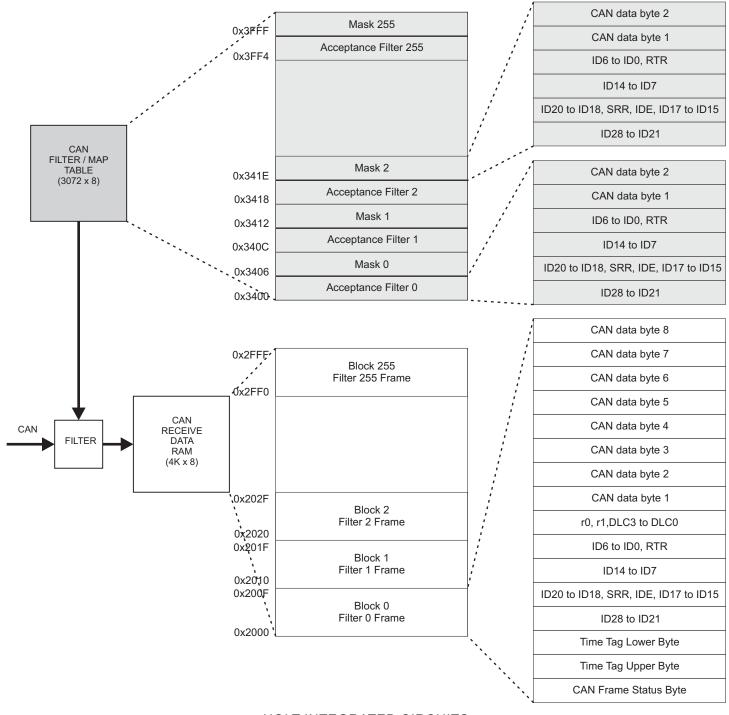

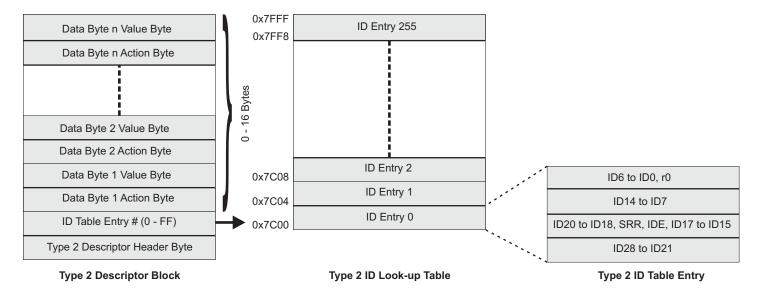

Received CAN frames are passed to the HI-3200 for filtering and storage. Each incoming frame's ID and first two data bytes is compared against a bank of up to 256 user-defined acceptance filters. If the frame meets the filter's acceptance criteria, it is stored in the CAN Received Data Memory. Each acceptance filter consists of a 6-byte match register and 6-byte mask. A frame is accepted if all unmasked bits match the corresponding bits in the frame. The frame is then written into the CAN received data memory location corresponding to the filter number.

Mask bits are defined as 1 = care and 0 = don't care. So for any given CAN frame bit to generate a filter pass condition, the received frame bit must equal the filter bit if the mask bit is "1", or any value if the mask bit is "0".

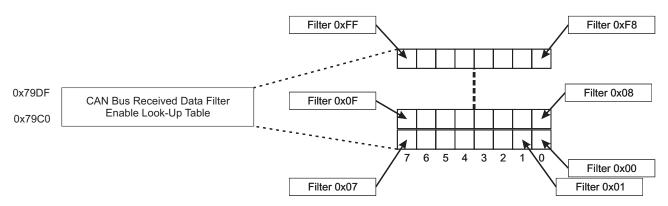

The number of filters active at any time is specified by writing a "1" into the corresponding bit position of the CAN Filter Enable look-up table. Only those filters identified as active in the table will be used to determine whether the frame is accepted.

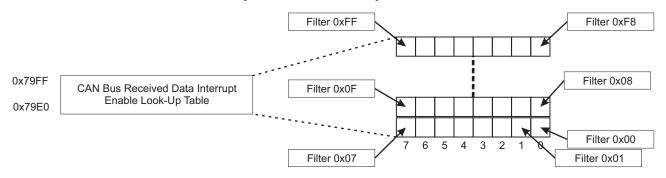

A CAN Receive Interrupt look-up table mirrors the active filter table. When a frame is accepted, and its corresponding Interrupt enable look-up bit is a one, then the CAN Interrupt bit is set in the Pending Interrupt Register. If the Interrupt Mask Register does not mask the CAN Interrupt, then the INT output signal will be asserted on frame reception and the CAN filter number will be loaded into the Interrupt Address Register.

It is possible that a received CAN frame may meet the acceptance criteria for more than one filter. In this case, only the first (lowest filter number) filter is used to qualify and store the incoming CAN frame.

The CAN Filter Enable look-up table, CAN Interrupt Enable look-up table, Filter and Mask definition tables must be loaded prior to turning on the CAN receiver, either via the host CPU interface or from the auto-initialization EEPROM.

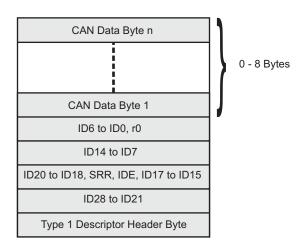

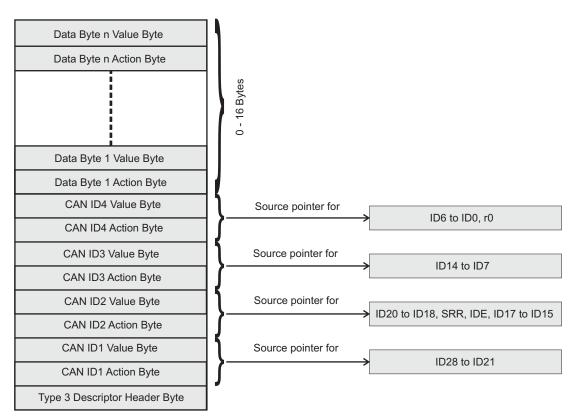

CAN frames are stored as sixteen-byte blocks as shown in the following diagram. Each block starts with a CAN frame Status Byte.

# **CAN Bus Received Data Filter Enable Look-Up Table**

### **CAN Bus Received Data Interrupt Enable Look-Up Table**

### CAN Received Data Filter, Filter Mask and Data Storage Organization

# **CAN Bus Received Data Status Byte Definition**

### CAN RECEIVED DATA BLOCK STATUS BYTE

| Bit | <u>Name</u> | R/W | <u>Default</u> | <u>Description</u>                                                                                                                                              |

|-----|-------------|-----|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | -           | R/W | 0              | Notused                                                                                                                                                         |

| 6   | -           | R/W | 0              | Notused                                                                                                                                                         |

| 5   | NEWHOST     | R/W | 0              | This bit is set when a new CAN frame is received and stored in this block. It is reset when the host CPU executes SPI instruction 0x9C to read the block.       |